- Simplified RISC CPU Design

Let's explore the simplified RISC CPU design.

2. RISC CPU Structure

4 Arithmetic Operators

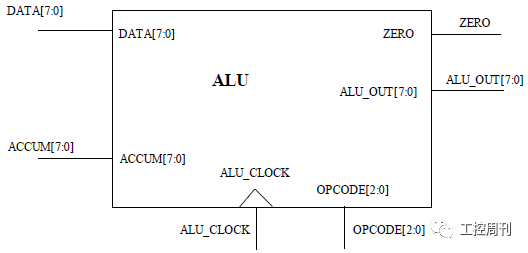

The Arithmetic Logic Unit (ALU) is designed to perform eight basic operations, including addition, AND, XOR, and jump, based on eight different operation codes. These fundamental operations can be combined to implement more complex functions, such as logical decisions or data manipulation. This approach simplifies the overall CPU architecture while maintaining flexibility in execution.

Below is the VerilogHDL code for the ALU module:

//------------------------------------------

Module alu (alu_out, zero, data, accum, alu_clk, opcode);

Output [7:0] alu_out;

Output zero;

Input [7:0] data, accum;

Input [2:0] opcode;

Input alu_clk;

Reg [7:0] alu_out;

Parameter HLT = 3'b000,

SKZ = 3'b001,

ADD = 3'b010,

ANDD = 3'b011,

XORR = 3'b100,

LDA = 3'b101,

STO = 3'b110,

JMP = 3'b111;

Assign zero = !accum;

Always @(posedge alu_clk)

Begin

// Operation code comes from the lower 3 bits of the instruction register output opc_iaddr[15..0]

Casex (opcode)

HLT: alu_out <= accum;

SKZ: alu_out <= accum;

ADD: alu_out <= data + accum;

ANDD: alu_out <= data & accum;

XORR: alu_out <= data ^ accum;

LDA: alu_out <= data;

STO: alu_out <= accum;

JMP: alu_out <= accum;

Default: alu_out <= 8'bxxxx_xxxx;

Endcase

End

Endmodule

//------------------------------------------

This simple implementation allows for efficient execution of common instructions, making it ideal for educational purposes or small-scale embedded systems. The use of a reduced instruction set ensures that each operation is executed quickly, with minimal complexity in the control logic. By focusing on essential functions, this RISC design provides a clear foundation for understanding how modern processors operate at a low level.

BANG KING WHOLESALE PRICE,BANG KING VAPE WHOLESALE

Shenzhen Essenvape Technology Co., Ltd. , https://www.essenvape.com