The development of sensor/scanning and computing technology is advancing the development of next-generation high-performance industrial inspection systems for various industries such as food processing, pharmaceuticals and semiconductor manufacturing, such as post-manufacturing quality assurance, metrology, robot vision and positioning. With the introduction of a new generation of digital signal processors (DSPs), especially multicore DSPs, developers will have high-performance, low-cost, low-power alternatives that enable real-time image processing implementations for inspection applications.

Today, industrial inspection systems require ever-increasing processing performance driven by various factors. The main reason for improving processing performance is that modern inspection systems not only run larger image data sets, but also execute more complex algorithms in real time. Multiple high-resolution (megapixel) and high frame rate (FPS) cameras are often required to provide large amounts of data, meaning that higher-end inspection systems can use multiple cameras to capture complete 3-D data, using depth cameras To capture depth shape information, or to generate surface contour information through a stereo camera.

Inspection system vendors typically implement product differentiation based on features implemented in software, particularly proprietary algorithms, which suppliers often cannot or do not want to use in system-on-a-chip (SoC) developed for many machine manufacturers for machine vision applications. Hardware accelerators, because doing so does not help them achieve performance or quality differentiation in the competition.

The following sections highlight the typical image processing algorithms used to inspect the system and the characteristics of the multicore DSP that provides the required processing efficiency.

Image processing:

At the heart of the inspection system are a variety of different image processing algorithms. These algorithms can be divided into several categories, such as image formation algorithms, image enhancement algorithms, morphological operations, feature extraction algorithms, and feature detection algorithms.

Image enhancement: It uses a nonlinear filter such as a median filter, a bilateral filter, and a histogram to remove noise and enhance edges and contrast. Edges are enhanced by algorithms such as non-enhanced masking or Sobel filtering, and Canny edge detectors can be used to obtain edges of important features in the image.

Morph operation: refers to the use of "structural elements" to interrogate images and provide various non-linear operations of the element structure's practical results in the image. This calculation can be used to thicken or thin the edges, remove small objects from large objects, join broken edges, eliminate small holes, and fill small gaps.

Most feature extraction and detection programs include edge detection, line tracking, object shape analysis, classification algorithms, and template matching. Sometimes images can be converted to different domains before extracting features, such as Fourier and Wavelet.

DSP is a powerful processing unit:

Both the image processing and data acquisition subsystems can achieve significant advantages through the use of DSPs. Homogeneous multicore DSPs provide processing performance that meets the needs of these computationally intensive algorithms.

Most industrial image processing subsystems require high performance in kernel speed (GHz), millions of instructions per second (MIPS), millions of multiply-accumulates per second (MMAC), and one billion floating-point operations per second (GFLOP). Multi-core processors such as the Texas Instruments TMS320C6678 support 360GMAC and 160GFLOPS, providing high flexibility for fixed-point instructions for systems requiring high dynamic range. To further improve system performance, the multi-core processor architecture also eliminates on-chip data transfer bottlenecks and latency issues through hardware-based interprocessor communication.

Multi-layer memory caches and available on-chip random access memory (RAM) capacity can greatly improve system performance. Image sizes typically far exceed the available on-chip RAM, so these systems inevitably require large external RAM, which means the DSP needs to provide a high-bandwidth external memory interface such as DDR3. The shared memory architecture allows multiple cores in a multicore DSP to run in parallel in different parts of the same image, or to perform different processing functions in the same portion of the image data. These features, combined with intelligent direct memory access controllers shared across all cores, enable data transfer between external memory, memory-mapped peripherals, and on-chip memory, and are double buffered for improved performance.

There are many options for connecting the imaging subsystem to the image processing subsystem. The system may require one or more analog or digital interfaces such as CameraLink. The DSP supports different high-speed serializer/deserializer interface options, providing hardware designers with connectivity and FPGA options to connect to the image acquisition subsystem. For example, the TI C6678 multicore DSP has multiple such high-speed interfaces, such as PCIe Gen II, Serial RapidIO 2.1 (SRIO), GigE, and TI's 50Gbps patented interface called Hyperlink. Sometimes images are sent through the backplane communication structure, and PCIe and SRIO are used.

Because industrial inspection systems often require a high degree of reliability to operate at the lowest power consumption under harsh conditions, multicore DSPs should support higher industrial operating temperature levels to help system designers design such systems.

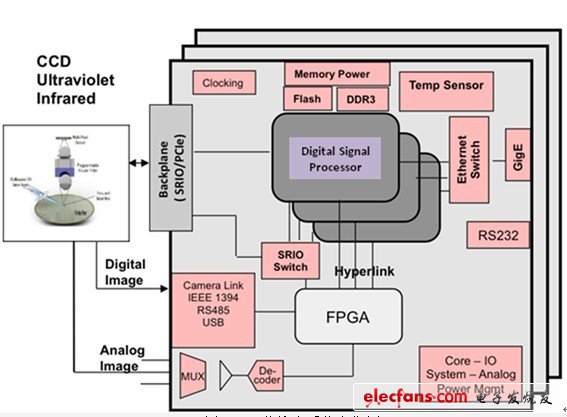

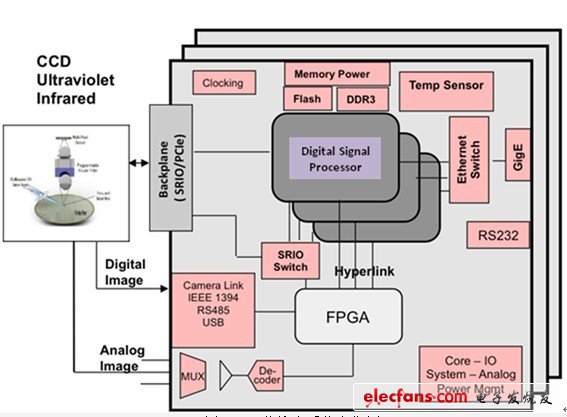

Figure 1 below is a schematic diagram of a multi-core DSP image processing subsystem.

Figure 1: Block diagram of the industrial inspection system

For more than 10 years, multicore DSPs have demonstrated their value in many different applications across industries. Multicore homogeneous DSPs have always been ideal for limited power budgets and small physical space applications that require computationally intensive signal processing. The latest generation of multi-core DSPs support superior computing performance, higher I/O, greater memory capacity, and major hardware integration to meet the needs of high-performance industrial inspections. The convenience of using a high-level language development software such as the C language to define an imaging system on the DSP accelerates the implementation of the latest innovative algorithms and reduces time-to-market.

Today, industrial inspection systems require ever-increasing processing performance driven by various factors. The main reason for improving processing performance is that modern inspection systems not only run larger image data sets, but also execute more complex algorithms in real time. Multiple high-resolution (megapixel) and high frame rate (FPS) cameras are often required to provide large amounts of data, meaning that higher-end inspection systems can use multiple cameras to capture complete 3-D data, using depth cameras To capture depth shape information, or to generate surface contour information through a stereo camera.

Inspection system vendors typically implement product differentiation based on features implemented in software, particularly proprietary algorithms, which suppliers often cannot or do not want to use in system-on-a-chip (SoC) developed for many machine manufacturers for machine vision applications. Hardware accelerators, because doing so does not help them achieve performance or quality differentiation in the competition.

The following sections highlight the typical image processing algorithms used to inspect the system and the characteristics of the multicore DSP that provides the required processing efficiency.

Image processing:

At the heart of the inspection system are a variety of different image processing algorithms. These algorithms can be divided into several categories, such as image formation algorithms, image enhancement algorithms, morphological operations, feature extraction algorithms, and feature detection algorithms.

Image enhancement: It uses a nonlinear filter such as a median filter, a bilateral filter, and a histogram to remove noise and enhance edges and contrast. Edges are enhanced by algorithms such as non-enhanced masking or Sobel filtering, and Canny edge detectors can be used to obtain edges of important features in the image.

Morph operation: refers to the use of "structural elements" to interrogate images and provide various non-linear operations of the element structure's practical results in the image. This calculation can be used to thicken or thin the edges, remove small objects from large objects, join broken edges, eliminate small holes, and fill small gaps.

Most feature extraction and detection programs include edge detection, line tracking, object shape analysis, classification algorithms, and template matching. Sometimes images can be converted to different domains before extracting features, such as Fourier and Wavelet.

DSP is a powerful processing unit:

Both the image processing and data acquisition subsystems can achieve significant advantages through the use of DSPs. Homogeneous multicore DSPs provide processing performance that meets the needs of these computationally intensive algorithms.

Most industrial image processing subsystems require high performance in kernel speed (GHz), millions of instructions per second (MIPS), millions of multiply-accumulates per second (MMAC), and one billion floating-point operations per second (GFLOP). Multi-core processors such as the Texas Instruments TMS320C6678 support 360GMAC and 160GFLOPS, providing high flexibility for fixed-point instructions for systems requiring high dynamic range. To further improve system performance, the multi-core processor architecture also eliminates on-chip data transfer bottlenecks and latency issues through hardware-based interprocessor communication.

Multi-layer memory caches and available on-chip random access memory (RAM) capacity can greatly improve system performance. Image sizes typically far exceed the available on-chip RAM, so these systems inevitably require large external RAM, which means the DSP needs to provide a high-bandwidth external memory interface such as DDR3. The shared memory architecture allows multiple cores in a multicore DSP to run in parallel in different parts of the same image, or to perform different processing functions in the same portion of the image data. These features, combined with intelligent direct memory access controllers shared across all cores, enable data transfer between external memory, memory-mapped peripherals, and on-chip memory, and are double buffered for improved performance.

There are many options for connecting the imaging subsystem to the image processing subsystem. The system may require one or more analog or digital interfaces such as CameraLink. The DSP supports different high-speed serializer/deserializer interface options, providing hardware designers with connectivity and FPGA options to connect to the image acquisition subsystem. For example, the TI C6678 multicore DSP has multiple such high-speed interfaces, such as PCIe Gen II, Serial RapidIO 2.1 (SRIO), GigE, and TI's 50Gbps patented interface called Hyperlink. Sometimes images are sent through the backplane communication structure, and PCIe and SRIO are used.

Because industrial inspection systems often require a high degree of reliability to operate at the lowest power consumption under harsh conditions, multicore DSPs should support higher industrial operating temperature levels to help system designers design such systems.

Figure 1 below is a schematic diagram of a multi-core DSP image processing subsystem.

Figure 1: Block diagram of the industrial inspection system

For more than 10 years, multicore DSPs have demonstrated their value in many different applications across industries. Multicore homogeneous DSPs have always been ideal for limited power budgets and small physical space applications that require computationally intensive signal processing. The latest generation of multi-core DSPs support superior computing performance, higher I/O, greater memory capacity, and major hardware integration to meet the needs of high-performance industrial inspections. The convenience of using a high-level language development software such as the C language to define an imaging system on the DSP accelerates the implementation of the latest innovative algorithms and reduces time-to-market.

Remote Trainer,Auto Trainer,Remote Collar,Best Remote Dog Training Collar

Elite-tek Electronics Ltd , https://www.aetertek.ca